Sâu bên trong chuỗi cung ứng, một số nhà ảo thuật biến cát thành những đĩa tinh thể silicon có cấu trúc kim cương hoàn hảo, là thành phần thiết yếu của toàn bộ chuỗi cung ứng chất bán dẫn. Chúng là một phần của chuỗi cung ứng chất bán dẫn giúp tăng giá trị của "cát silicon" lên gần một nghìn lần. Ánh sáng mờ nhạt mà bạn thấy trên bãi biển chính là silicon. Silicon là một tinh thể phức tạp, giòn và giống kim loại rắn (tính chất kim loại và phi kim loại). Silicon có ở khắp mọi nơi.

Silic là vật liệu phổ biến thứ hai trên Trái Đất, sau oxy, và là vật liệu phổ biến thứ bảy trong vũ trụ. Silic là chất bán dẫn, nghĩa là nó có tính chất điện giữa chất dẫn điện (như đồng) và chất cách điện (như thủy tinh). Một lượng nhỏ các nguyên tử lạ trong cấu trúc silic có thể thay đổi cơ bản hành vi của nó, do đó độ tinh khiết của silic cấp bán dẫn phải cao đến mức đáng kinh ngạc. Độ tinh khiết tối thiểu được chấp nhận đối với silic cấp điện tử là 99,999999%.

Điều này có nghĩa là chỉ có một nguyên tử không phải silicon được phép cho mỗi mười tỷ nguyên tử. Nước uống tốt cho phép có 40 triệu phân tử không phải nước, ít tinh khiết hơn 50 triệu lần so với silicon cấp bán dẫn.

Các nhà sản xuất wafer silicon trống phải chuyển đổi silicon có độ tinh khiết cao thành các cấu trúc tinh thể đơn hoàn hảo. Điều này được thực hiện bằng cách đưa một tinh thể mẹ đơn vào silicon nóng chảy ở nhiệt độ thích hợp. Khi các tinh thể con mới bắt đầu phát triển xung quanh tinh thể mẹ, thỏi silicon sẽ từ từ hình thành từ silicon nóng chảy. Quá trình này diễn ra chậm và có thể mất một tuần. Thỏi silicon thành phẩm nặng khoảng 100 kg và có thể tạo ra hơn 3.000 wafer.

Các tấm wafer được cắt thành các lát mỏng bằng dây kim cương rất mịn. Độ chính xác của các công cụ cắt silicon rất cao và người vận hành phải được giám sát liên tục, nếu không họ sẽ bắt đầu sử dụng các công cụ để làm những điều ngớ ngẩn với mái tóc của mình. Phần giới thiệu ngắn gọn về quá trình sản xuất tấm wafer silicon quá đơn giản và không ghi nhận đầy đủ những đóng góp của các thiên tài; nhưng hy vọng sẽ cung cấp nền tảng để hiểu sâu hơn về hoạt động kinh doanh tấm wafer silicon.

Mối quan hệ cung cầu của tấm silicon

Thị trường wafer silicon do bốn công ty thống trị. Trong một thời gian dài, thị trường đã ở trong trạng thái cân bằng tinh tế giữa cung và cầu.

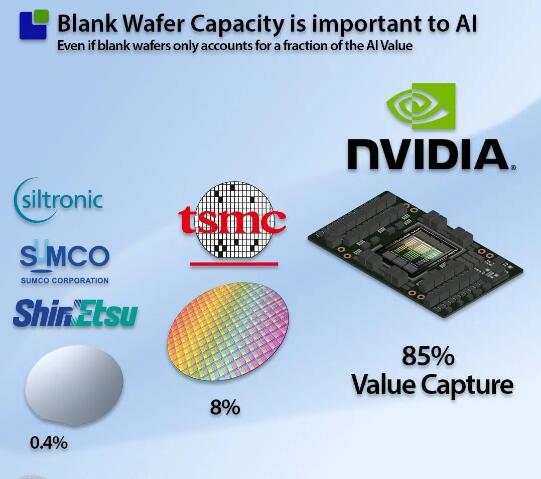

Doanh số bán chất bán dẫn giảm vào năm 2023 đã khiến thị trường rơi vào tình trạng cung vượt cầu, khiến lượng hàng tồn kho bên trong và bên ngoài của các nhà sản xuất chip ở mức cao. Tuy nhiên, đây chỉ là tình trạng tạm thời. Khi thị trường phục hồi, ngành công nghiệp sẽ sớm quay trở lại ngưỡng công suất và phải đáp ứng nhu cầu bổ sung do cuộc cách mạng AI mang lại. Quá trình chuyển đổi từ kiến trúc dựa trên CPU truyền thống sang điện toán tăng tốc sẽ tác động đến toàn bộ ngành, như Tuy nhiên, điều này có thể tác động đến các phân khúc giá trị thấp của ngành công nghiệp bán dẫn.

Kiến trúc Bộ xử lý đồ họa (GPU) đòi hỏi nhiều diện tích silicon hơn

Khi nhu cầu về hiệu suất tăng lên, các nhà sản xuất GPU phải vượt qua một số hạn chế về thiết kế để đạt được hiệu suất cao hơn từ GPU. Rõ ràng, làm cho chip lớn hơn là một cách để đạt được hiệu suất cao hơn, vì các electron không thích di chuyển quãng đường dài giữa các chip khác nhau, điều này hạn chế hiệu suất. Tuy nhiên, có một hạn chế thực tế khi làm cho chip lớn hơn, được gọi là "giới hạn võng mạc".

Giới hạn in thạch bản là kích thước tối đa của một con chip có thể được phơi sáng trong một bước duy nhất trên máy in thạch bản được sử dụng trong sản xuất chất bán dẫn. Giới hạn này được xác định bởi kích thước từ trường tối đa của thiết bị in thạch bản, đặc biệt là máy bước hoặc máy quét được sử dụng trong quy trình in thạch bản. Đối với công nghệ mới nhất, giới hạn mặt nạ thường là khoảng 858 milimét vuông. Giới hạn kích thước này rất quan trọng vì nó xác định diện tích tối đa có thể được tạo hoa văn trên tấm wafer trong một lần phơi sáng. Nếu tấm wafer lớn hơn giới hạn này, sẽ cần nhiều lần phơi sáng để tạo hoa văn đầy đủ cho tấm wafer, điều này không thực tế đối với sản xuất hàng loạt do những thách thức về độ phức tạp và căn chỉnh. GB200 mới sẽ khắc phục được giới hạn này bằng cách kết hợp hai chất nền chip có giới hạn kích thước hạt thành một lớp xen kẽ silicon, tạo thành một chất nền siêu giới hạn hạt có kích thước gấp đôi. Các giới hạn hiệu suất khác là dung lượng bộ nhớ và khoảng cách đến bộ nhớ đó (tức là băng thông bộ nhớ). Các kiến trúc GPU mới khắc phục được vấn đề này bằng cách sử dụng bộ nhớ băng thông cao xếp chồng (HBM) được lắp trên cùng một bộ xen kẽ silicon với hai chip GPU. Theo quan điểm của silicon, vấn đề với HBM là mỗi bit của diện tích silicon gấp đôi DRAM truyền thống do giao diện song song cao cần thiết cho băng thông cao. HBM cũng tích hợp một chip điều khiển logic vào mỗi ngăn xếp, làm tăng diện tích silicon. Một phép tính sơ bộ cho thấy diện tích silicon được sử dụng trong kiến trúc GPU 2.5D gấp 2,5 đến 3 lần so với kiến trúc 2.0D truyền thống. Như đã đề cập trước đó, trừ khi các công ty đúc chuẩn bị cho sự thay đổi này, công suất wafer silicon có thể lại trở nên rất eo hẹp.

Năng lực tương lai của thị trường wafer silicon

Quy luật đầu tiên trong ba quy luật sản xuất chất bán dẫn là cần phải đầu tư nhiều tiền nhất khi có ít tiền nhất. Điều này là do bản chất chu kỳ của ngành và các công ty bán dẫn gặp khó khăn khi tuân theo quy tắc này. Như thể hiện trong hình, hầu hết các nhà sản xuất wafer silicon đã nhận ra tác động của sự thay đổi này và đã tăng gần gấp ba tổng chi tiêu vốn hàng quý của họ trong vài quý vừa qua. Bất chấp điều kiện thị trường khó khăn, điều này vẫn đúng. Điều thậm chí còn thú vị hơn là xu hướng này đã diễn ra trong một thời gian dài. Các công ty wafer silicon rất may mắn hoặc biết điều gì đó mà những công ty khác không biết. Chuỗi cung ứng chất bán dẫn là một cỗ máy thời gian có thể dự đoán tương lai. Tương lai của bạn có thể là quá khứ của người khác. Mặc dù chúng ta không phải lúc nào cũng nhận được câu trả lời, nhưng chúng ta hầu như luôn nhận được những câu hỏi có giá trị.

Thời gian đăng: 17-06-2024